You may have come across many ordinary transistor gain tester circuits designs, but this specific circuit will help you to determine the gain of high frequency RF transistors quickly with some quick potentiometer adjustments.

Circuit Working

The gain of a transistor under high frequency will depend on the DC bias factors through which it functions. This is because the optimum gain is obtained at just one specific level of collector current.

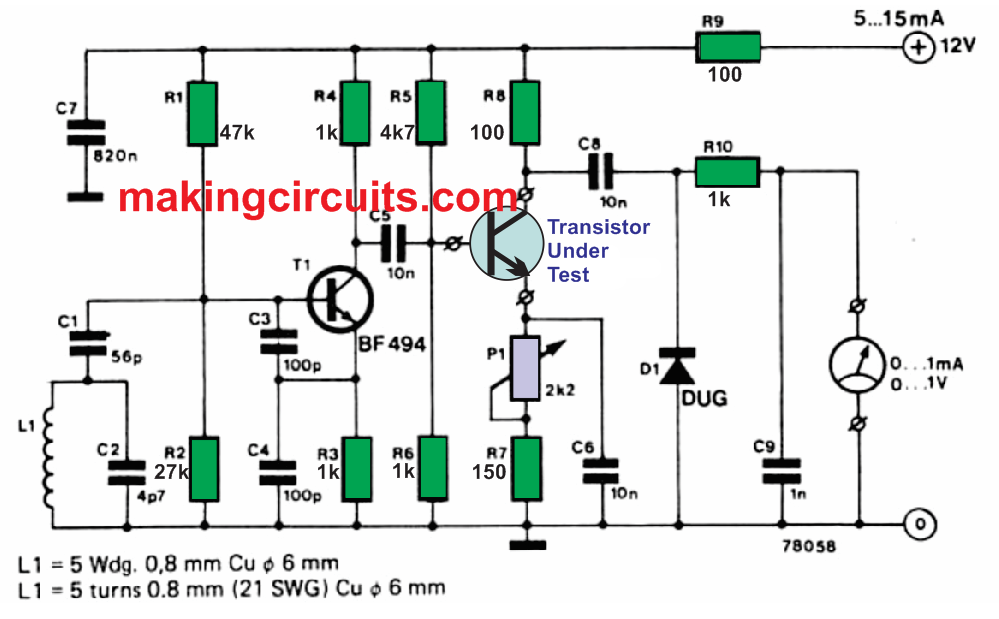

This simple transistor gain circuit as shown above was created to find out the best collector current for a given NPN RF transistor.

The transistor which is being analyzed is introduced directly into an amplifier stage that is applied with a fixed amplitude of 100 MHz signal through an oscillator stage configured around T1.

This particular oscillator signal is amplified by the transistor under test, rectified by D1 and filtered by R1O and C9 to provide a DC signal relative to the RF signal output of the transistor under test.

This, subsequently, will be proportional to the current gain of the transistor being tested. The collector current from the test transistor could be tweaked from 1 mA and 10 mA through preset P1, that must be installed with a linearly calibrated scale having these specified values.

Once this is done it is a easy job to fine-tune P1 until the optimum output voltage is received over the meter, where upon the most effective collector current could be measured directly from the P1 calibrated scale dial.

Leave a Reply