Any time we think about regarding a set-up of electronic assemblies or repairs, it is typical to possess to have some test equipmentwhich is able to produce a specified amount of adjustable current. We could, no doubt, use power resistors that we can configure as per various series or parallel combinations, however this quickly turns into annoying due to its limitations. Additionally, no continuous adjustment is achievable, being forced to have a significant range of power resistances, making things rather troublesome. The circuit idea proposed here can be effectively used as an adjustable curent stage in any amateur laboratory, mainly because it enables to fix this matter in a really amazing way while keeping a low cost price.

It acts, essentially, as an electronic adjustable current from 0 to 10 A in a couple of ranges.

Therefore it can absorb any current between these two confines and with any voltage placed on it that is between 3 and 80V. To sum it up, this construction addresses the majority of the regular requirements in this field.

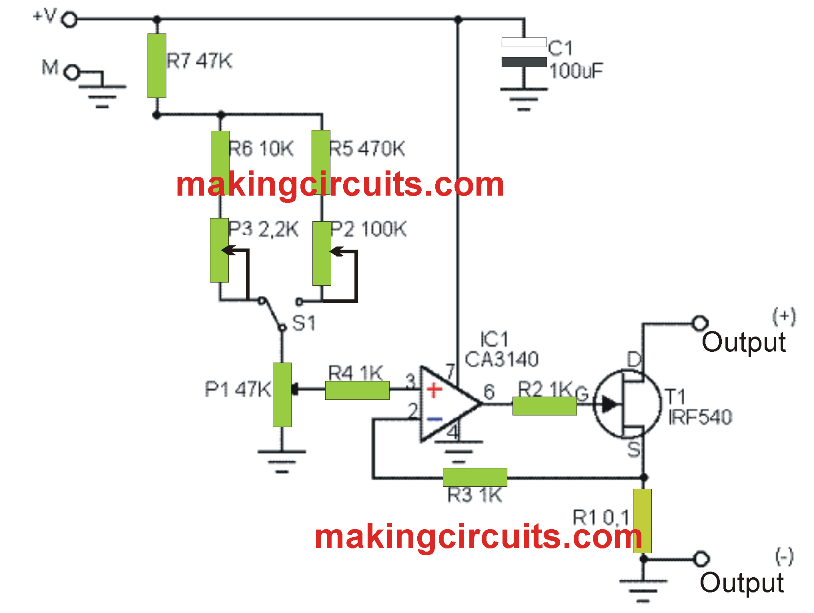

The theory of the design is pretty easy to comprehend once you analyze your circuit diagram. The actual load is constituted by the MOS transistor, or T1, which will be pretty much conductive working on its gate voltage. To determine the current that travels through it and, consequently, the current that is consumed by the load, the voltage drop which it produces across the low value resistance R1 is referred upon by the opamp.

The IC2 integrated circuit, is rigged as an enhanced zener by incorporating some electronics, which lets an incredibly stable voltage of 1.2V to be developed at its terminals. This voltage is generated the non-inverting input of IC1 following attenuation by different voltage divider stages to resistors and potentiometers.

The inverting input of IC1 obtains the voltage deduced on the terminals of R1; voltage that is, as a result, proportional to the current consumed by the connected load. According to the standard rule of the operational amplifier, the latter then generates an output voltage that, takes care to ensure almost that all of its input voltages, causes T1 roughly conductive with respect to the demands. The switch S1 enables to have 2 working ranges employing a voltage division rate governed by IC2 pretty much significant. The potentiometer P1 deduces an adjustable fraction of this voltage, thereby permitting a continuous adjustment of current to the sine of the selected range.

Parts List

IC1: CA3140

IC2: ICL8069

T1: IRF540

R1: 0.1 20 W

R2 to R4: 1K 1 / 4W 5%

R5: 470K 1 / 4W 5%

R6: 10K 1 / 4W 5%

R7: 47K 1 / 4W 5%

C1: 100uF / 25V

P1: rotary linear potentiometer to be implanted over IC of 47 K

P2: vertical adjustable potentiometer for CI of 100K

P3: vertical adjustable potentiometer for IC of 2.2K

S1: switch 1 circuit, 2 positions.

There seems to be a problem with posting or approval, hopefully this time this goes through.

Several other respondents have pointed out that there is no IC2 in this circuit, and I’m in agreement there. Without it (or something similar – a TL431 could be used, though there are additional bits necessary), this circuit is VERY dependent upon the stability of the OpAmp supply voltage (the voltage introduced at the upper left hand side of the schematic). If you change the OpAmp supply voltage, the voltage at the non-inverting OpAmp voltage will change, and that will result in a change in the expected value from the Current Sense.

Also, as the text is written, it does NOT point out that the V+ input is from a separate supply than the + Output. This is important, since the CA3140 OpAmp is not going to manage an 80V input – it tops out at 36V, this circuit as presented would need two power supplies, at least if you expect to drive the ouput very high

As others have also pointed out, the output(+) is really whatever voltage you are supplying your load with (i.e. the circuit as shown is not OUTPUTTING +V there), and the load needs to be between that and the Drain (top side of the IRF540 N-FET in your schematic), and the Drain pin is effectively the GND for your load. The PSUs for the load AND for your OpAmp, and the voltage dividers all need to be tied to a common ground, but the load itself should not be – this circuit is modulating the GND of the load. The mosfet is acting as a large variable resistor. For that reason, the mosfet really should be affixed to a suitable heat sink.

I have a similar circuit but use a resistor and zener to regulate the voltage for the OpAmp side from a common supply (since the OpAmp itself needs very little current), and use two OpAmp channels (an LM358 works fine), one to amplify the voltage drop across an 0R01 (10 mOhm) resistor and input that to the inverting input of the other OpAmp channel which drives the FET (an IRF2807, though the 13mOhm Rds(on) is a bit of a waste when I’m actively limiting current). It works quite well for driving things such as LCD backlights for verification and repair.

The Vgs of the transistor should not be overlooked – if the OpAmp is supplied by something higher than that, it is possible that the OpAmp will try to drive the gate harder than is permitted. So, while the OpAmp here can manage 36V, the specific FET can only handle ±20Vgs. If your load is running at less than the setpoint (or isn’t connected), the smoke might be let out of the FET. So, plan to ensure your OpAmp is regulated to below the Vgs of your FET, and that will protect the FET.

By using a current sense that is much lower resistance, it results in a lower voltage drop, and consequently less dissipation. At 10A a 10mOhm resistance will dissipate 1W, which is still a lot, but it is 1/10 of what the circuit presented here will dissipate. In my case, while the other components could handle it, I don’t run higher than a couple of amps for the stuff I test with the circuit I built, so the current sense is fractions of a watt. If the voltage dividers have range limiting, you can’t overshoot the setpoint and TRY to drive too much current.

BTW, here’s a 20W R10: https://www.arrow.com/en/products/rto020fr1000jte3/vishay

and a 1W R01: https://www.arrow.com/en/products/tlr2h10dr01ftdg/te-connectivity

I can adjust my circuit down to a few tens of microamps (µA) of current, and generally run it from a 48V PSU

The operation of this circuit will have the OpAmp trying to achieve feedback from the current sense resistor to match the output from the setpoint (via the voltage dividers). This will drive the FET full on if the load doesn’t happen to actually pull the specified current – say a microcontroller that is driving something else you want to limit current through. If your load is sensitive to voltages, this could be a problem.

Angry elephant, go to the woods and show your anger on the trees….

You Go through the diagram…… and say where is your load to be connected. Please Check it man……. If your description goes this way……all angry elephants and lions will leave the forest in search of you….????????????

Go through your circuit and description once more …..

Load is connected to the (+)output. Ground wire of the load goes to the (+)output and the positive wire of the load goes to the positive supply line

On drain IRF 540 is not positive,it is minus

the load will need to be connected across the positive and the drain

Dear Sirs, where do I connect the IC2 in the circuit above ? would you please help?

Thanks in anticipation