The article talks about the pinout activity as well as other crucial specs of the IC 4043. Let's find out about the total datasheet of this quite interesting chip.

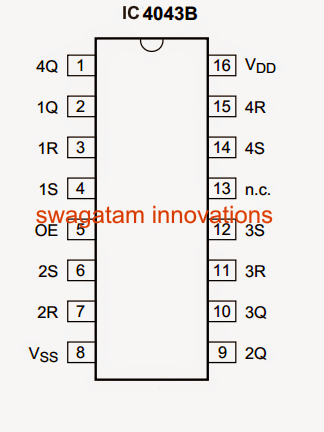

Pinout Datasheet of IC 4043

Theoretically the IC 4043 is a quad set/reset (R/S) latch with 3 logic state output.

To become more accurate this chip has 4 sets of inputs (which means 8 input pinouts) and 4 related single outputs.

The 4 sets of inputs are comprised of 4 pairs of set/reset inputs.

For each and every set/reset we certainly have one corresponding output.

Each one of these set reset inputs react to high logic signals, producing a bistable impact at their related output pinouts.

Bistable describes flip flop action, quite simply a high pulse to the "set" input makes the corresponding output high from its original low state, and a high to the reset input reverts the above state from high back to low state.

Consequently essentially to create a corresponding outputs high, we have to employ a high on their "set" inputs and to make the outputs low once again we simply require to use an additional high to their reset inputs.

The working of the input and output pinouts are as easy as that.

Furthermore, the IC has one more fascinating input pinout OE which happens to be a common output enable pinout.

For allowing the above described set/reset actions in the IC, this OE input ought to be associated with logic high or simply just with Vdd (supply votage).

In the above circumstance the output is permitted with the stipulated flip flop functioning.

If the OE input is linked with ground, the output freezes and generates a high impedance reply, that is neither demonstrates a low output nor a high, rather locks input a unresponsive blocked state, therefore the name 3 logic state output.

Thus the OE input may be used to turn off the IC working if essential to a specific application.

The IC is most effective with supply voltages from 5 to 15V.

Let's sum up the input output pinout benefits and requirements of the IC 4043 with the following information:

1Q to 4Q (Pins: 2, 9, 10, 1) 3-state buffered latch output

1R to 4R (Pins: 3, 7, 11, 15) reset input (active HIGH)

1S to 4S (Pins: 4, 6, 12, 14) set input (active HIGH)

OE (Pin:5) common output enable input

VSS (Pin: 8) ground supply voltage

N.C. (Pin: 13) not connected

VDD (Pin: 16) supply voltage

Leave a Reply